|

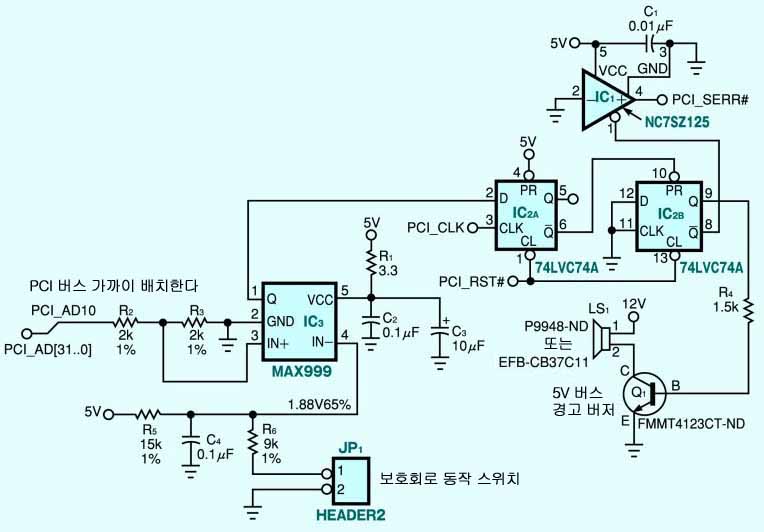

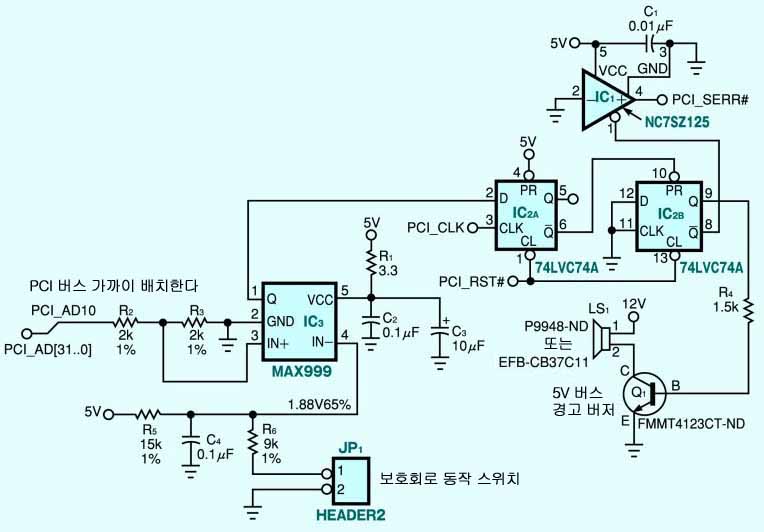

그림 1의 회로는 전압을 자동적으로 검출하여, 3.3V

대응의 PCI와 같은 버스를 5V 진폭의 신호로부터 보호하는 회로이다. 보호 다이오드나 종단저항을 이용해서 적절한 종단전압을 설정하면 1버스사이클 이내에서 버스의 신호진폭을 어떤 값으로 설정하는 회로로서도 사용할 수 있다.

최근의 VLSI 기술은 가공 치수가 「딥 서브미크론」이라고 하는 영역에 도달했다. 이 때문에 이러한 기술로 제조하는 IC는

입출력부의 진폭이 3.3V로 제한되는 경우가 있다. 이 IC와 5V의 버스를 탑재하는 카드

등을 접속하면 IC에 손상을 주고만다.

그림 1의 회로는 1 버스사이클 이내에서 진폭이 3.3V보다 큰 신호를 정확하게 검출한다. 과전압을 검지했을 때에는 알람과

리셋 신호를 출력하여 유저와 시스템 양쪽으로 모두 알린다.

이 회로의 특징은 4가지가

있다. 첫째는 동기하여 과전압을 검출할 수

있으므로 신호가 오버슛에 의해 전압이 높아져도 알람을 출력하지 않는다는 점, 둘째는 버스에 대해서 임피던스가 높고, 용량이 작은

부하로서 동작한다는 점, 셋째는 과전압을 검출했을 경우에 시스템을 자동적으로 슛다운 할 수 있다는 점, 넷째는 응답시간이 1 버스

사이클보다

짧다는 점이다.

이 회로는 미국 이퀘이터 테크놀로지스사(www.equator.com)의 동작전압이 3.3V인 프로세서「MAP-CA」패밀리와 조합하여

동작을 확인했다. 동작전압이 3.3V 이하의

시스템에도 적용이 가능하다. 이퀘이터사의 최신 칩은 동작전압이 3.3V라도 5V 진폭의 신호에 견딜 수 있다. 그러나, 동작전압이 1.8V나 2.5V 이외의

칩에서는 보호가 필요하다.

IC3에는 전달지연시간(TPD)이 4.5 ns로

짧은 미국

맥심 인티그레티드 프로덕트사(www.maxim-ic.com)의 비교기 IC MAX999」를 사용했다. PCI 버스 신호선 중의

1선(PCI_AD10)으로 3.8V의 기준전압을 항상 비교하고 있다. 이 기준전압이면 5V신호가 3.3V의 보호 다이오드에

의해 클램프되었을 때의 전압인지, 통상적인 3.3V의 동작전압인지를 판별할 수 있다. 신호전압이 이 기준전압을 1 버스사이클에 걸쳐 넘었을 경우에 회로는 트랜지스터 Q1에 접속한 알람·버저를

울린다.

이 회로는 리셋 신호를 시스템에 출력할 수 있다. 이 신호는 시스템의 오류검출신호로도 사용할 수 있다. 알람용 레지스터

IC2B는 비동기형이다. 이 때문에 알람은 시스템에서 IC2B에 공급하는 전력을 정지하든가, 리셋 신호를 입력하여 해제한다.

신호의 overshoot이나

undershoot 현상으로 잘못하여 트리거가 걸리지 않도록

하기 위해 플립플롭 논리를 기본으로 한 레지스터

IC2A는 버스 클록신호의 상승 에지에서 비교기 IC의 출력을 받아들인다. 이 방법을 이용하면 일반적인 버스클록 신호 주파수인 33MHz에 있어서의 33 ns

주기내에서 신호가 안정화되고 나서 보호회로로서 동작하게 된다.

IC3의 3번 핀에 있어서 3p~5pF의 기생용량과 검출저항인 R2와 R3으로 구성되는 저대역 통과 필터에 의해 이 회로에서 대응할 수 있는 최대 클록신호 주파수가

정해진다. 따라서, IC3의 3번 핀과 R2, R3 사이의 배선을 짧게 하면 이 회로에서 대응할 수 있는 주파수를 최대 40M~50MHz로

할 수 있다. 게다가 R2와 R3의 저항값을 대칭성을 유지하면서 작게 하면 버스의 동작

주파수는 이론적으로는 최대 140MHz

이상(주기는 7 ns)으로 할 수 있다. 그러나 이 경우 버스의 부하전류가 커져 버린다.

PCI 버스에 이 회로를 실제로 적용하기

위해서는 비교기 IC3의 3번 핀을 PCI_AD10 신호와 접속하면 된다. PCI 버스를 사용하고 있는 기기는 다른 기기를 검출할

경우에 반드시 한번은 이 신호를 사용하기 때문이다. 다른 신호를 동시에 관측함으로써

동일한 기능을 실현할 수 있다. 그러나 PCI_AD10

신호를 감시하는 것만으로도,BIOS가 시스템을

부트할 경우에 다른 기기를 검출하는 동작을 실행할 수 있다. 이 때문에 5V 대응의 PCI 버스를 사용한 기기를 찾아낼 수 있다.

5V

대응의 PCI 버스를 사용한 기기가 접속되었을 경우, 비교기 IC3의 1번 핀(출력 Q)은 PCI 버스 클록신호의 상승

에지에서

IC2A를 latch-on한다. 이렇게 해서 플립플롭 논리의 레지스터 IC2B가 동작하게 된다. 이 결과, 버저 LS1가 울림과

동시에 IC1의

오픈 컬렉터를 통해 음논리의 오류검출신호가 시스템에 출력된다. 이 오류검출신호를 이용하여 자동적으로 시스템을 정상화하는 기능도 실현할 수

있다. 이 경우, 고장난 회로를 동작시키지 않도록 한다.

검출저항 R2와 R3, 기준전위 생성용 저항 R5와 R6은 공칭오차가

1%의

금속피막저항을 사용할 필요가 있다. R5에 입력하는 5V의 기준전압이 비교기 IC의 임계값 확도를 결정한다. 최근의 전압 레귤레이터

IC는 충분한 전압확도가 있으므로 시스템의 5V 전원을 기준전압원으로 사용할 수 있다. 즉 별도로 5V

기준전압을 준비할 필요는 없다.

점퍼(보호회로 동작 스위치) JP1를 해제하면 이 회로의 동작을 무효로 할 수 있다.

|

[그림 1]

사용자에게

과전압을 알리는 회로

과전압을 검출했을 경우에 버저를 울림과 동시에 시스템에 대해서 오류검출신호를 출력한다.

PCI_AD10를 입력신호에 이용했다.

| |