|

이 아이디어에서는 I2C

버스를 5~0 V의 진폭(플러스 도메인)으로부터 0~-5V의

진폭(마이너스 도메인)으로 변환하는 방법을 소개한다.

복수의 전원전압을 가지는 시스템에서는 진폭이 0~5V의 디지털 논리 신호를 마이너스

전원에서 동작하는 아날로그 신호로 변환하는 경우가 있다. 실현 수단으로는

플러스 도메인으로 D-A 변환을 실시하고 나서 전압변환하는 방법이 있다. 그러나, 이 방법에서는 오차가 발생한다.

게다가 부품수도 많아져 버린다. 이 방법보다 디지털 신호의 전압 변환을 실시하고 나서 마이너스

도메인으로

D-A 변환을 실행하는 편이 좋다. 다만 이 경우는 마이너스 기준

전압원을 준비할 필요가 있다.

I2C

버스는 2선식의 쌍방향 버스다. 1선은

클락선이고, 또 1선은 데이터선이다. pull-up 저항과 오픈 컬렉터에 의해, 음논리의 신호를 출력할

수 있게 된다.

|

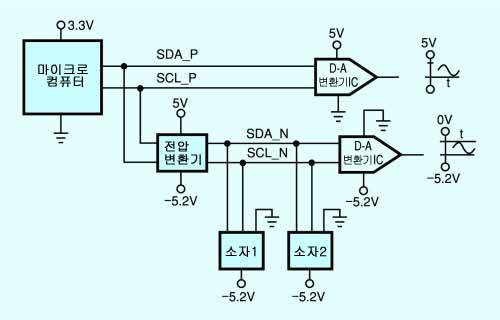

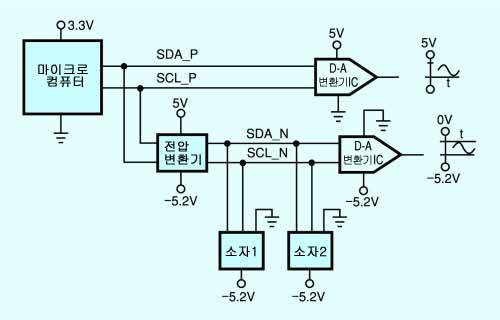

[그림 1]

I2C 버스를 사용한 전형적인 회로

구성

마이크로컴퓨터가 마스터로, 다른 주변소자가 슬레이브이다. 각각의 소자는

개별적으로 I2C

주소를 가진다.

|

그림 1에는 I2C

버스를 사용한 전형적인 회로 구성을 나타낸다. 마이크로컴퓨터가

마스터로, 다른 주변 소자가 슬레이브이다. 각각의 소자는 개별적으로 I2C

주소를 가진다. 마스터가 항상 클록신호를 생성한다. 마스터와

슬레이브의 양쪽 모두가 데이터선을 사용해 데이터를 송신할 수 있는 구성으로

되어 있다.

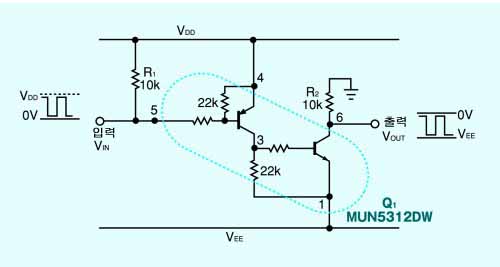

전압 변환의

동작을 그림 2에 나타낸 간단한 회로를 사용하여 설명한다. 이 회로는 클록신호를 플러스로부터

마이너스의 전압으로

변환한다. IC Q1은 pnp 트랜지스터와 npn 트랜지스터, 4개의 저항을 내장하고

있으며, 패키지는

SOT-363이다. 저항 R1은 플러스 도메인에 필요한 풀업 기능을 제공한다. 마이너스

도메인에서는 저항 R2가

이 기능을 담당한다.

|

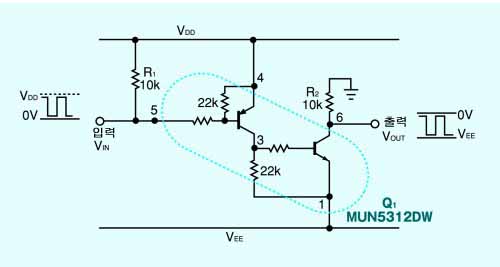

[그림 2]

전압 변환회로의 예

이 회로는 플러스

전압으로부터

마이너스 전압으로 변환할 수 있지만, 마이너스 전압에서

플러스 전압으로는 변환할 수 없다.

|

그림 2의

회로 동작은 간단하다. 입력전압 VIN를 VDD로 설정하면 Q1는 오프 상태로 된다. 따라서 출력전압

VOUT=0V이다(논리는 하이레벨). VIN를 0V로 설정하면 Q1은 온 상태로 바뀌므로

VOUT=VEE로 된다(논리는 로우레벨). 이 회로는 플러스로부터 마이너스의 방향으로만 전압을 변환한다. 이 때문에

마스터는 슬레이브가 클록신호를 로우레벨로 유지하고 있는 것을 확인할 수 없다. 따라서, I2C

버스의 클록선에 있어서의 확장 기능(대기상태)을 이용하려는

경우는 쌍방향(플러스에서 마이너스와, 마이너스에서 플러스로의

방향)으로 전압 변환할 수 있는 회로가 필요하게 된다.

데이터선에도 쌍방향으로 전압 변환할 수 있는 회로가 필요하다. 마스터가 데이터를 송신할 때, 마스터는

마이너스 도메인에 있는 슬레이브가 데이터의 9비트째를 로우레벨에 풀다운했는지,

그 여부를 확인한다. 이 동작을 송신

데이터의 1바이트마다 실행할 필요가 있다. 슬레이브가 마스터의 지시를 받아 데이터를 송신하는 경우도

마찬가지이다. 슬레이브가 데이터 송신 모드일 때, 슬레이브는 마스터가 데이터의 9비트째를 로우레벨에 풀다운 했는지,

그 여부를 송신 데이터의 1바이트마다 확인해야 한다.

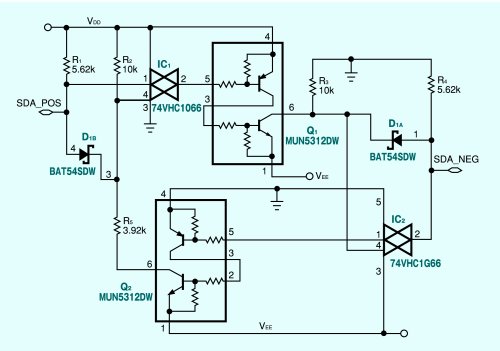

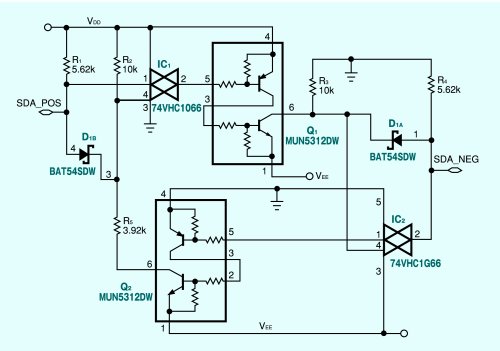

이러한 동작도 5개의 IC와 5개의 저항만으로

실현 가능하다(그림 3). 그림 3의 회로는 그림 2의 회로와 회로 토폴러지가 같다. 아날로그

스위치

IC1과 아날로그 스위치 IC2를 온 상태로 함과 동시에 그림 3에 나타낸 회로의 하반

부분을

무시하고 생각하면

된다.

|

[그림 3]

쌍방향으로 전압을 변환할 수 있는 회로

이

회로는 플러스 전압에서 마이너스 전압으로의 변환과 마이너스

전압에서 플러스 전압으로의 변환, 양쪽 모두에 대응할 수 있다.

|

SDA_POS 핀을 VDD로 설정하면 IC Q1은 오프 상태로 된다.

따라서 저항 R3과 저항 R4가 출력을 0V에 pull-up 한다. 이 때문에 SDA_NEG=0V로

된다(논리는 하이레벨). SDA_POS 핀을 0V로 설정하면 Q1은 온 상태로 바뀌므로

SDA_NEG≒VEE로 변화한다(논리는 로우레벨).

여기서 슬레이브에서

마스터로의 데이터 송신 경로를

설명한다. SDA_NEG 핀을 0V로 설정하면(논리는 하이레벨), IC Q2는 오프 상태로 됨과 동시에

저항 R1은 SDA_POS 핀을 VDD까지 풀업한다. SDA_NEG 핀을 VEE로

설정하면(논리는 로우레벨), Q2는 온 상태로 된다. 이 결과, 저항 R1과 저항 R2, 저항 R5에 의해

출력전압이 결정된다. 여기서는 SDA_POS≒0V이다. R1과 R2, R5의 각각의 저항값은 VDD=5V와 VEE=-5.2V의 두가지

조건에 의해 정해진다. 귀환경로에 트랜지스터를 추가하면 논리를 나타내는 전압값을

R1과 R2, R5의 저항값으로부터 독립적으로 설정할 수도 있다.

마스터/슬레이브가 SDA_POS

핀/SDA_NEG 핀을 풀다운(논리는 로우레벨)할 때, 아날로그 스위치 IC1과 아날로그

스위치 IC2, 쇼트키 배리어 다이오드 D1A, 쇼트키 배리어

다이오드 D1B는 정귀환의 경로를 차단하는 역할을 담당한다. 이러한

소자가 없으면 Q1이나 Q2는 latch 동작을 하고만다.

그림 3의 회로는 클록 주파수가 50kHz인 I2C 버스의 타이밍에 관한 사양을 만족시킨다.

클록 주파수를 100kHz로 높이고 싶다면 내부저항이 10kΩ인「MUN5311」를 Q1과 Q2에 사용하면 된다. 「MUN5312」의 내부저항은 22kΩ다.

클록선에도 그림 3의 회로를 채용하면 모든 I2C

버스 모드의 동작을 실현할 수 있게 된다. |